Cómo una empresa japonesa fundada en 1927 se convirtió en una pieza imprescindible en la industria de los chips avanzados

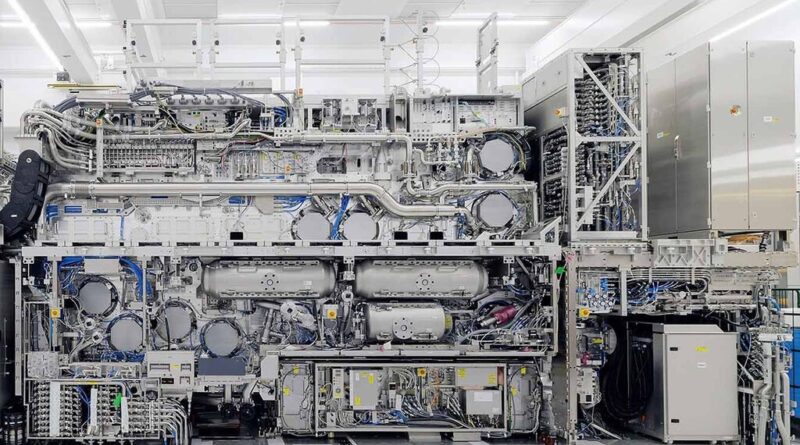

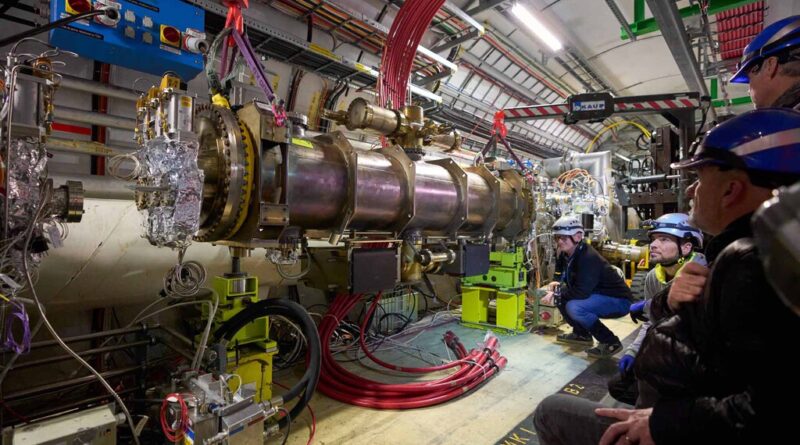

Mucho hemos hablado de la importancia de ASML para la industria de los semiconductores. La empresa holandesa es la única que suministra los equipos de fotolitografía ultravioleta extremo (UVE) para la fabricación de chips avanzados. Sin esta tecnología, cuyos competidores como Canon y Nikon abandonaron porque el esfuerzo para desarrollarla era demasiado grande, no habríamos podido sobrepasar la barrera de los 5 nanómetros en materia de transistores.

En el complejo y enraizado sector de la fabricación de los chips que dan vida a teléfonos inteligentes, ordenadores, centros de datos y otros dispositivos, ASML no es el único actor esencial. Hay otras empresas cuya aportación es clave y difícilmente reemplazable. La japonesa Valqua es una de ellas. Sus productos, no obstante, no contienen miles de piezas, cables y software integrado. La empresa se especializa en la fabricación de tanques extremadamente limpios.

La clave está en la personalización y la limpieza

Pese a que las soluciones de Valqua no son comparables a nivel de complejidad con otras que forman parte de la industria de los semiconductores, esta empresa fundada hace casi un siglo prácticamente no tiene competencia. Según Bloomberg, es el proveedor de depósitos de almacenamiento de químicos más grande del mundo y, por si esto fuera poco, uno de sus clientes más importantes es Taiwan Semiconductor Manufacturing Company (TSMC).

Y cuando hablamos de TSMC, hablamos de otro gigante. Los taiwaneses dominan el mercado de los semiconductores de manera aplastante, con más del 50% de este, escoltado por Samsung. Ahora bien, ¿por qué esta empresa casi desconocida es una piedra angular en la fabricación de chips? Su historia es de lo más interesante. De acuerdo a su propia página web, fue fundada en 1927 y sus primeros productos fueron pastillas de frenos para coches.

La gran pericia de su equipo de técnicos e ingenieros permitió a los directivos de la empresa ir ampliando paulatinamente su catálogo de productos. En 1932 empezaron a fabricar juntas para uso industrial. La calidad que manejaban era destacable, por lo que también ingresaron al a industria de la aviación suministrando juntas de caucho sintético y láminas comprimidas para aeronaves. En un ascenso imparable, en 1962 llegaron a la segunda sección de la Bolsa de Tokio.

En los años posteriores, la dirección de la empresa japonesa se enfocó en consolidar su presencia en el extranjero y estableció subsidiarias en China, Taiwán, Corea del Sur, Vietnam y Estados Unidos. Al mismo tiempo continuó desarrollando su oferta de soluciones, añadiendo la posibilidad de que los clientes solicitaran tanques de acero a medida. Y esto último era un gran diferencial en torno a la competencia ya que buscaba satisfacer una necesidad puntual de la industria de chips.

Las fábricas de chips requieren de cientos de depósitos de químicos de diferentes tamaños, los cuales varían de acuerdo a las necesidades de cada fabricante. En otras palabras, no hay una medida estandarizada. Por esta razón, flexibilidad de Valqua para hacer tanques con características personalizadas es una enorme ventaja. Estos pueden tener hasta 4 metros de diámetro, 9 metros de altura y suelen tener una vida útil de 10 años.

Estos tanques son utilizados para almacenar productos químicos para la fabricación de semiconductores. Y sabemos muy bien que los entornos en los que se fabrican los chips, como la fábrica de Intel que visitamos en Israel, se caracterizan por ser extremadamente limpios. La presencia de partículas de polvo pueden acabar arruinando las obleas y, mucho peor aún, algunos de los costosos equipos de AMSL.

Por consecuencia, la fabricación de este producto en particular de Valqua requiere de un protocolo específico. La compañía recubre el interior de los depósitos con fluororesina con trabajadores cualificados y con la indumentaria adecuada. Estos también se encargan de revestir las tuberías que se conectan a los depósitos. Y todo el proceso se lleva a cabo en un ambiente extremadamente limpio.

“Una impureza a nivel molecular haría inútil toda la solución química en un tanque, ya que degradaría drásticamente los rendimientos de producción de la fabricación de chips de vanguardia”, señala el presidente de Valqua, Yoshihiro Hombo. Además asegura que la capacidad que tienen para fabricar y transportar sus tanques libres de impurezas “no es algo que se pueda imitar fácilmente”.

La compañía japonesa, como mencionamos arriba, dio sus primeros pasos como fabricante de frenos para coches. Hoy es una pieza clave de la industria de los semiconductores. De hecho, más de la mitad de sus ingresos provienen de este sector que, por cierto, parece no tener freno. Desde Valqua apuntan a alcanzar un crecimiento de un 30% en sus ventas en los próximos cuatro años.

En Xataka | Microsoft lleva años preparando el lanzamiento de sus propios chips. Y ya tiene aliado estrella: Intel

*Una versión anterior de este artículo se publicó en marzo de 2023

-

La noticia

Cómo una empresa japonesa fundada en 1927 se convirtió en una pieza imprescindible en la industria de los chips avanzados

fue publicada originalmente en

Xataka

por

Juan Carlos López

.